ターゲットを独立させたのはJTAGKey2Pを接続して使いたいためです。

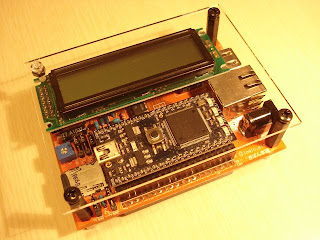

ここでは実際にLPCXpresso LPC1768にJTAGKey2Pを接続してみました。

OpenOCDはgitリポジトリから2010/12/12現在のものを取り出して使用しました。

まずはOpenOCDのビルドです。JTAGKey2Pではlibftd2xxを使用します。

http://www.ftdichip.com/Drivers/D2XX.htm

2010/12/12現在のバージョンはlibftd2xx1.0.0.tar.gzです。

ダウンロードして展開しておきます。

tar xvfz libftd2xx1.0.0.tar.gz

次にOpenOCDのソースコードです。

git clone git://openocd.git.sourceforge.net/gitroot/openocd/openocd

cd openocd

./bootstrap

./configure --enable-ft2232_libftdi --with-ftd2xx-linux-tardir=/path/to/libftd2xx1.0.0

makeビルドにはautomakeも必要です。

予めビルド環境に入れておいてください。

ビルドできたらmake installして出来上がりです。

ここで試しにsuikanさんがポーティングされたTOPPSER/ASP for LPCのバイナリをOpenOCD経由でフラッシュに書き込んでみましょう。

まずはOpenOCDを起動します。

その前に・・・OpenOCDの設定ファイルを確認します。

openocd.cfgは以下のようにしました。

source [find /usr/local/share/openocd/tcl/interface/jtagkey2p.cfg]

source [find /usr/local/share/openocd/tcl/target/lpc1768.cfg]jtagkey2p.cfgはgitリポジトリに入っている物と同じです。

lpc1768.cfgについてはSWDを使う設定になっていました。

これについては以下のように修正して使用しました。

# NXP LPC1768 Cortex-M3 with 512kB Flash and 32kB+32kB Local On-Chip SRAM,

# # LPC17xx chips support both JTAG and SWD transports.

# # Adapt based on what transport is active.

# source [find target/swj-dp.tcl]

if { [info exists CHIPNAME] } {

set _CHIPNAME $CHIPNAME

} else {

set _CHIPNAME lpc1768

}

# After reset the chip is clocked by the ~4MHz internal RC oscillator.

# When board-specific code (reset-init handler or device firmware)

# configures another oscillator and/or PLL0, set CCLK to match; if

# you don't, then flash erase and write operations may misbehave.

# (The ROM code doing those updates cares about core clock speed...)

#

# CCLK is the core clock frequency in KHz

if { [info exists CCLK ] } {

set _CCLK $CCLK

} else {

set _CCLK 4000

}

if { [info exists CPUTAPID ] } {

set _CPUTAPID $CPUTAPID

} else {

set _CPUTAPID 0x4ba00477

}

#delays on reset lines

adapter_nsrst_delay 200

jtag_ntrst_delay 200

# LPC2000 & LPC1700 -> SRST causes TRST

reset_config srst_pulls_trst

jtag newtap $_CHIPNAME cpu -irlen 4 -expected-id $_CPUTAPID

#swj_newdap $_CHIPNAME cpu -irlen 4 -expected-id $_CPUTAPID

set _TARGETNAME $_CHIPNAME.cpu

target create $_TARGETNAME cortex_m3 -chain-position $_TARGETNAME

# LPC1768 has 32kB of SRAM In the ARMv7-M "Code" area (at 0x10000000)

# and 32K more on AHB, in the ARMv7-M "SRAM" area, (at 0x2007c000).

$_TARGETNAME configure -work-area-phys 0x10000000 -work-area-size 0x8000

# LPC1768 has 512kB of flash memory, managed by ROM code (including a

# boot loader which verifies the flash exception table's checksum).

# flash bank (name) lpc2000 (base) (size) 0 0 (target#) (variant) (clock) [calc checksum]

set _FLASHNAME $_CHIPNAME.flash

# flash bank $_FLASHNAME lpc2000 0x0 0x80000 0 0 $_TARGETNAME lpc1700 $_CCLK calc_checksum

flash bank $_FLASHNAME lpc2000 0x0 0x80000 0 0 $_TARGETNAME lpc1700 120000

# Run with *real slow* clock by default since the

# boot rom could have been playing with the PLL, so

# we have no idea what clock the target is running at.

jtag_khz 500

$_TARGETNAME configure -event reset-init {

# Do not remap 0x0000-0x0020 to anything but the flash (i.e. select

# "User Flash Mode" where interrupt vectors are _not_ remapped,

# and reside in flash instead).

#

# See Table 612. Memory Mapping Control register (MEMMAP - 0x400F C040) bit description

# Bit Symbol Value Description Reset

# value

# 0 MAP Memory map control. 0

# 0 Boot mode. A portion of the Boot ROM is mapped to address 0.

# 1 User mode. The on-chip Flash memory is mapped to address 0.

# 31:1 - Reserved. The value read from a reserved bit is not defined. NA

#

# http://ics.nxp.com/support/documents/microcontrollers/?scope=LPC1768&type=user

mww 0x400FC040 0x01

}

init

reset init次にOpenOCDを起動します。

shinta@greenpad:~/Projects/ledblink_lpcxpresso_1768$ sudo openocd

[sudo] password for shinta:

Open On-Chip Debugger 0.5.0-dev-00651-gc6e0705 (2010-12-11-21:58)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.berlios.de/doc/doxygen/bugs.html

Info : only one transport option; autoselect 'jtag'

adapter_nsrst_delay: 200

jtag_ntrst_delay: 200

none srst_pulls_trst

500 kHz

Info : max TCK change to: 30000 kHz

Info : clock speed 500 kHz

Info : JTAG tap: lpc1768.cpu tap/device found: 0x4ba00477 (mfg: 0x23b, part: 0xba00, ver: 0x4)

Info : lpc1768.cpu: hardware has 6 breakpoints, 4 watchpoints

Info : JTAG tap: lpc1768.cpu tap/device found: 0x4ba00477 (mfg: 0x23b, part: 0xba00, ver: 0x4)

Warn : Only resetting the Cortex-M3 core, use a reset-init event handler to reset any peripherals無事に起動したらtelnet localhost 4444でOpenOCDと接続します。

halt, flash probe 0, flash write_image erase (バイナリファイル名), resetでLPCXpresso LPC1768上にあるLEDがチカチカする事を確認してみましょう。

shinta@greenpad:~$ telnet localhost 4444

Trying ::1...

Trying 127.0.0.1...

Connected to localhost.

Escape character is '^]'.

Open On-Chip Debugger

> halt

> flash probe 0

flash 'lpc2000' found at 0x00000000

> flash write_image erase /home/shinta/Projects/ledblink_lpcxpresso_1768/asp.bin

auto erase enabled

wrote 32768 bytes from file /home/shinta/Projects/ledblink_lpcxpresso_1768/asp.bin in 5.705619s (5.609 KiB/s)

> reset

JTAG tap: lpc1768.cpu tap/device found: 0x4ba00477 (mfg: 0x23b, part: 0xba00, ver: 0x4)

Only resetting the Cortex-M3 core, use a reset-init event handler to reset any peripheralsOpenOCD側の端末ではクライアントから受けたコマンドの動作が記されていると思います。

target state: halted

target halted due to debug-request, current mode: Thread

xPSR: 0x01000000 pc: 0x1fff0080 msp: 0x10001ffc

Info : accepting 'telnet' connection from 4444

flash 'lpc2000' found at 0x00000000

auto erase enabled

wrote 32768 bytes from file /home/shinta/Projects/ledblink_lpcxpresso_1768/asp.bin in 5.705619s (5.609 KiB/s)

Info : JTAG tap: lpc1768.cpu tap/device found: 0x4ba00477 (mfg: 0x23b, part: 0xba00, ver: 0x4)

Warn : Only resetting the Cortex-M3 core, use a reset-init event handler to reset any peripheralsこの文書ではLPCXpresso LPC1768をJTAGKey2Pで使用するための狭い範囲のドキュメントとして作成しました。

TOPPERS/ASP for LPCに関するドキュメントはsuikanさんがお書きになった以下のドキュメントも参照してください。